同步电路和跨时钟域设计

亚稳态

什么是同步电路?

电路中的所有受时钟控制的单元,全部由一个统一的全局时钟控制。

- 优点:EDA工具可以保证电路系统时序收敛,有效避免了电路设计中竞争冒险现象;触发器在时钟边沿取值,很大限度地减少了整个电路受毛刺和噪声影响的可能。

- 缺点:时钟偏斜;时钟抖动;增加面积和功耗。

什么是异步电路?

电路中的数据传输可以在任何时候发生,没有一个全局或者局部的时钟控制。

- 优点:模块化;对信号延迟不敏感;没有时钟偏斜问题;潜在的高性能;好的电磁兼容;低功耗。

- 缺点:设计复杂;缺少响应的EDA工具支持;在大规模集成电路设计中应该避免采用异步电路设计。

亚稳态是指触发器无法在规定的时间内达到一个可确认的状态。亚稳态不能从根本上消除,但可以采取措施降低对电路的影响。

$$

MTBF = \frac{ e^{ t_{MET} / C_2 } }{C1 f{CLK} f{DATA} }

$$

上式是对$MTBF$故障间隔平均时间的描述,值越大,电路稳定性越好。其中,$t{MET}$表示寄存器从时钟上升沿触发后的时序余量时间,$f{CLK}$表示接受时钟域的时钟频率,$f{DATA}$表示数据变化频率。$C_1$和$C_2$是器件相关参数。

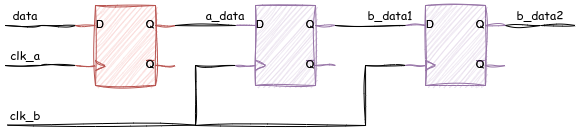

双锁存器电平同步器

双锁存器电平同步器如下:

用两个锁存器,以增大$MTBF$。

- 优点:结构简单、易实现。

- 缺点:增加了两级触发器延时;当快时钟域转到慢时钟域,易造成采样丢失。

单bit信号跨时钟域传输

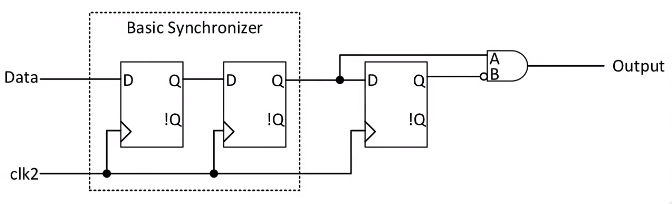

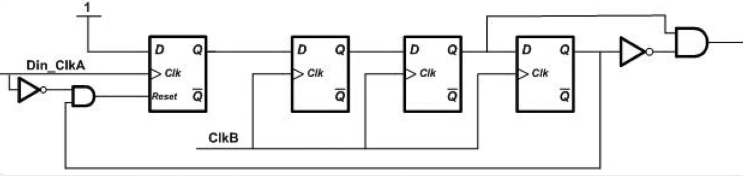

边沿检测同步器电路

适用场景:慢时钟域到快时钟域。输入数据的宽度必须比一个时钟周期加上一个同步触发器的hold时间要长。

对于慢时钟域的一个时钟周期,快时钟域可能已经过了多个时钟周期,但是边沿只会变化一次。所以该方法的入手点在这里。

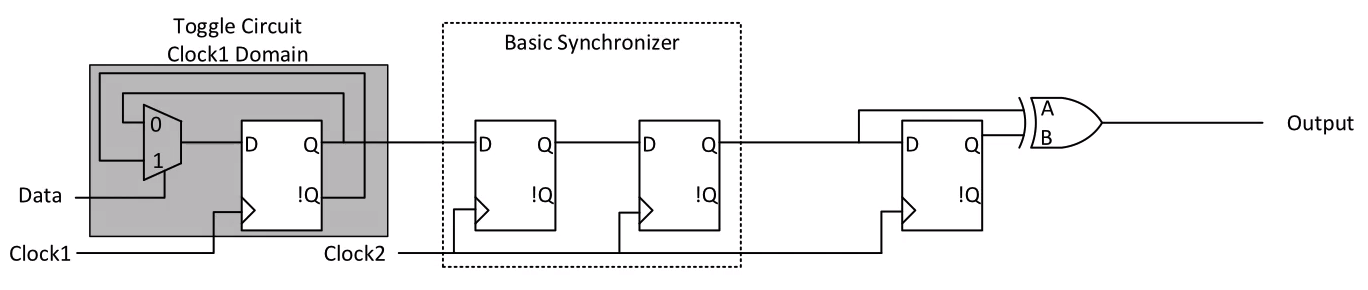

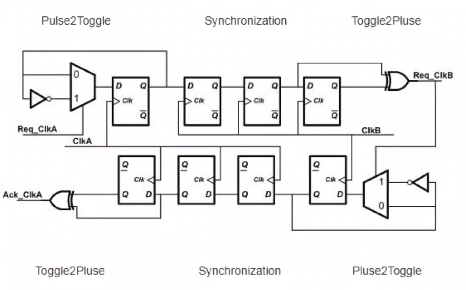

脉冲同步器

适用场景:快时钟域到慢时钟域。输入脉冲之间的最小间隔必须等于两个同步器的时钟周期。

核心是翻转电路,两次输入信号不同的时候,翻转电路输出值为1;反之,输出为0。

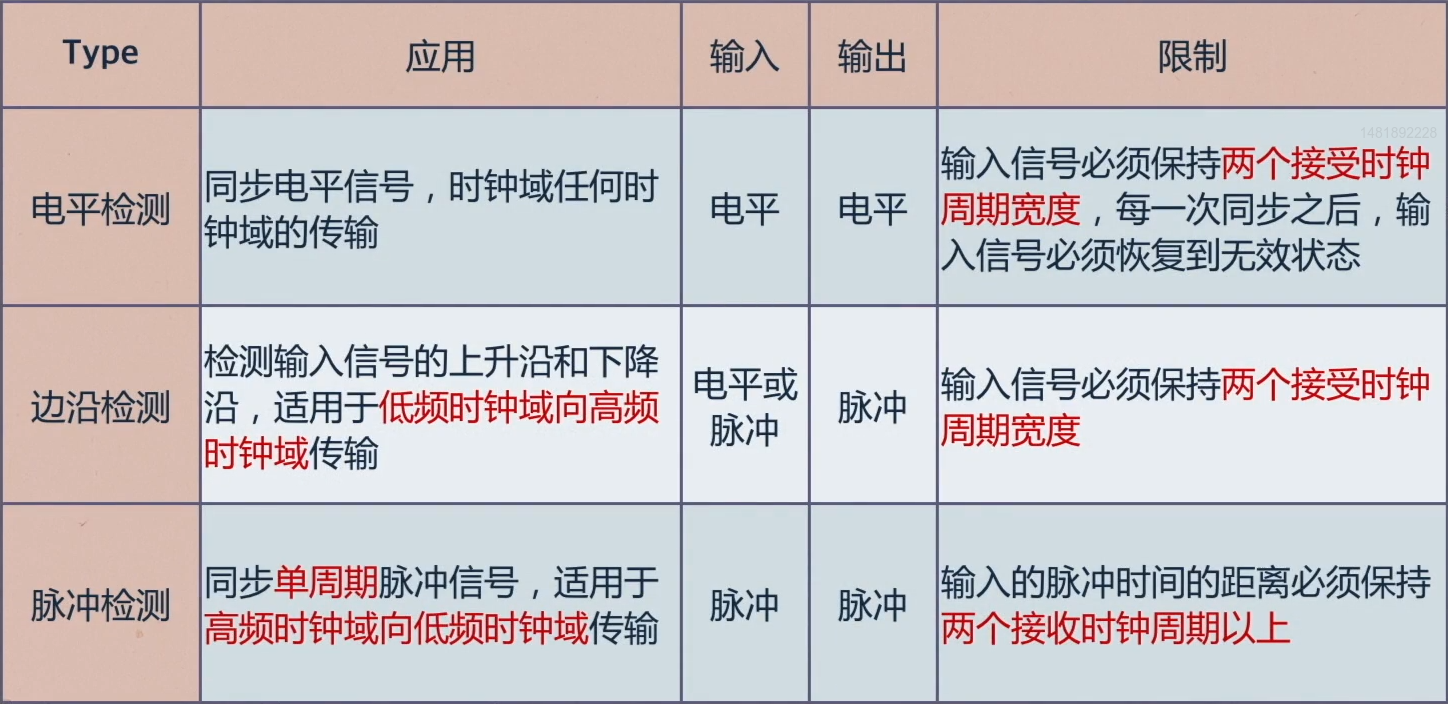

三种同步器比较

结绳法

问题背景:

信号从快时钟域到慢时钟域的时候,慢时钟可能无法对变化太快的信号实现正确采样。

结绳法适合任何时钟域的过渡。共有三种实现方式。

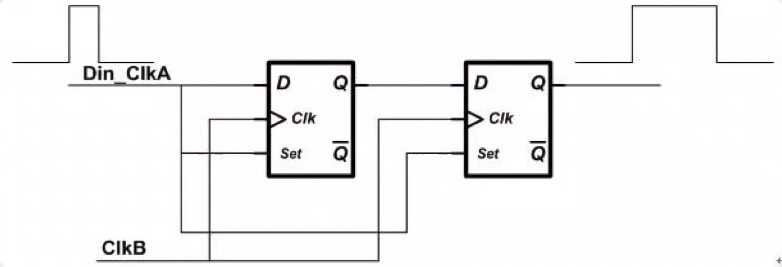

第一种实现方式:

利用B的采样数据作为异步复位信号。

适用条件:传输数据少,且脉冲间隔大。要求$T_a > 3T_b$。

第二种实现方式:

利用数据作为异步复位信号。

第三种实现方式:

利用握手协议。

总结

适用场景:快时钟到慢时钟。原理就是将单脉冲延长,以方便采样到数据。

两类方法:

- 脉冲边沿做时钟。

- 脉冲电平做选择器或者异步复位、置位。

结绳法实现复杂,效率不高,设计性能要求较高的场合慎用。

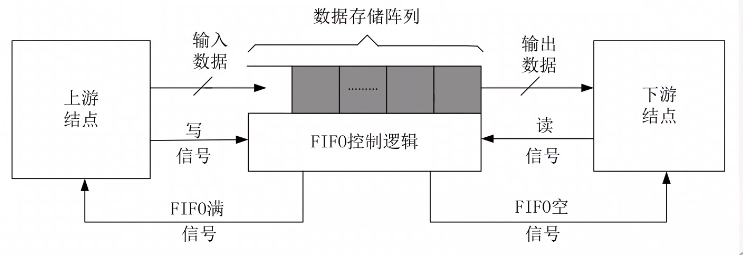

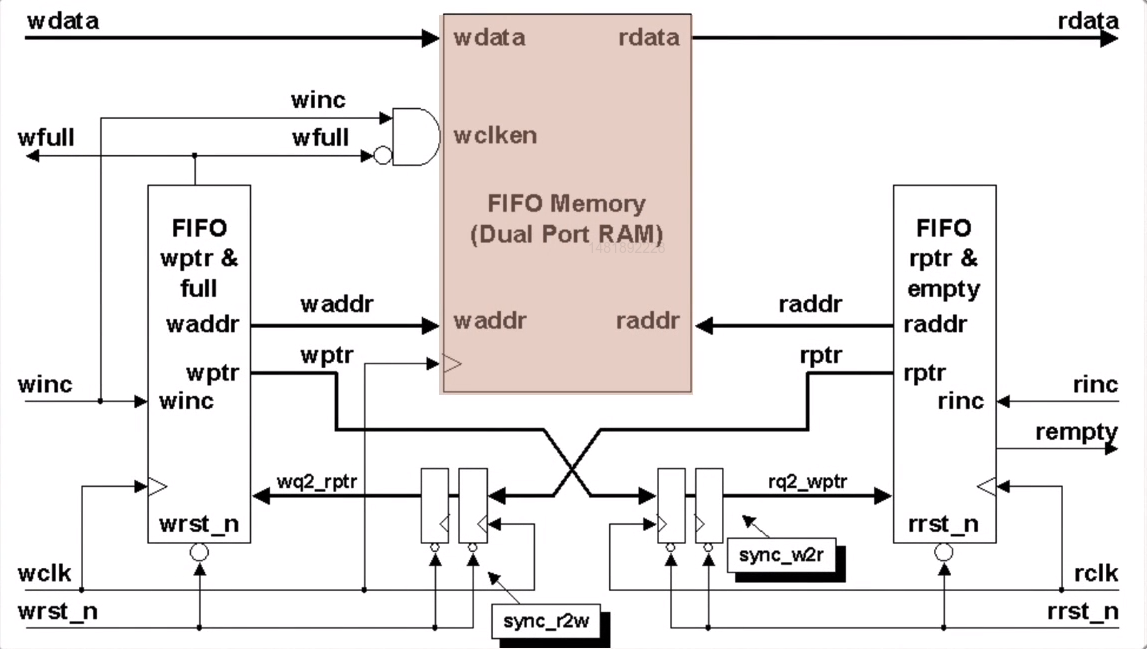

FIFO

解决多bit数据跨时钟域传输。

先进先出的存储结构,功能简单。但受限与顺序读和顺序写。

两个用处:

- 异步FIFO:两个不同时钟域的数据快速,便捷的传输。

- 不同位宽的传输。

常见参数

- FIFO的深度:可以存储的数据的个数。

- FIFO的宽度:一次读写数据的宽度

- 满标志:FIFO已满或者是将要满的时由FIFO的状态电路送出的一个信号,以防止FIFO写溢出。

- 空标志:FIFO已空或者是将要空的时由FIFO的状态电路送出的一个信号,以防止FIFO的无效数据读出。

- 读时钟:读操作所遵循的时钟。

- 写时钟:写操作所遵循的时钟。

空满信号

正确的产生空满标志是FIFO设计的关键。写满而不溢出,能读空而不多读。

在地址中添加一个额外的位,当写指针增加并越过最后一个FIFO地址时,就将写指针这个未用的MSB加1,其他为回零。对读指针也进行同样的操作。

- 如果两个指针的MSB不同,其他位相同,则表示已满。

- 如果两个指针的MSB相同,其他位相同,则表示已空。

如果使用普通的连续数列判断读写位置,在变化的时候,可能会产生亚稳态。在这里,我们使用格雷码来传输。

格雷码的生成

原数的最高位不变,低位数和次低位数相互异或得到该低位的值。

格雷码空满判断:

- 两者完全相等的时候,则已空。

- 读写指针MSB不同;次高位不同,其他位相同,则已满。

FIFO深度设置

FIFO的深度要满足重载时候的需求,即背靠背情况。

$$

depth = burst_length – \frac{burst_length}{wclk} \times (rclk \times \frac{X}{Y})

$$

其中,写时钟频率为$wclk$,读时钟频率为$rclk$,写时每B个时钟周期内会有A个数据写入FIFO,读时每Y个时钟周期都会有X个数据读出FIFO。

对于$burst_length$:

$$

burst_length = 2 \times \frac{A}{B}

$$

具体取值视情况而定。

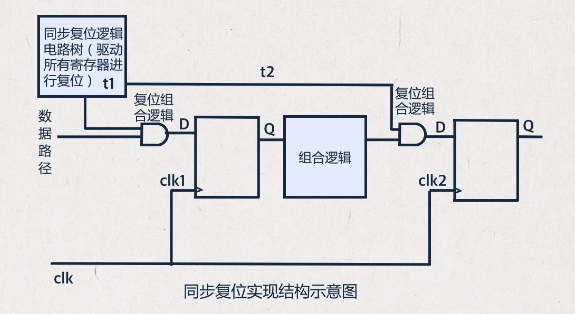

复位电路

复位电路,使仿真时电路进入初始状态或者其他预知状态;对于综合实现的电路,通过复位使电路进入初始状态或者其他预知状态。

同步复位

只有时钟边沿采样到复位信号后,才进行复位。

- 优点:有利于仿真器仿真;可以使系统成为100%同步时序电路,有利于时序分析;可以过滤高时钟频率的毛刺。

- 缺点:复位信号必须大于时钟周期;大多数DFF都是异步复位。

异步复位

当复位信号有效沿到达时,无论时钟沿是否有效,都会立即对目标进行复位。

- 优点:节约逻辑资源;设计简单;识别方便,很方便使用FPGA的全局复位端口GSR。

- 缺点:复位信号释放的时候容易出现问题;容易受到毛刺影响。

异步复位同步释放

复位信号不需要与时钟同步,释放时必须和时钟信号同步。结合了同步复位和异步复位的优点。

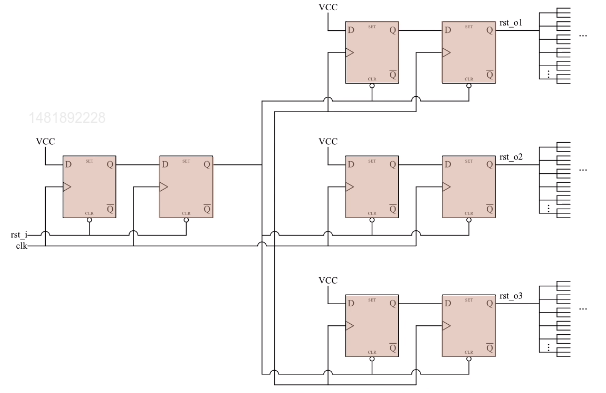

复位分发技术

收到复位信号后,先对复位信号进行同步,然后在分发到各个子复位网络中的时候,再进行一次复位信号同步。

状态机

基本要素

状态,输入,输出

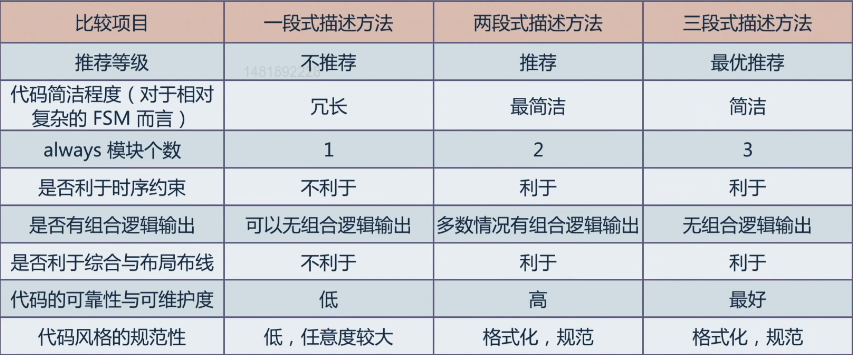

什么是RTL级好的FSM描述?

- FSM要安全,稳定性高。

- FSM要速度快,满足设计的频率要求。

- FSM面积小,满足设计的面积要求。

- FSM的设计要清晰易懂、易维护。

写法:一段式,两段式,三段式。三种模式的比较如下:

参考资料

- MOOC芯加速设计——第3章