逻辑综合

1 概述

1.1 目的

- 决定电路门级结构

- 寻求时序和面积的平衡

- 寻求功耗与时序的平衡

- 增强电路的测试性

1.2 阶段

三个阶段如下:

1.3 处理对象

- Design:整个需要被综合的电路。

- Port:整个

design最外部的端口。 - Clock:时钟。一定要单独处理!

- Cell:被例化的模块。

- Pin:

cell的引脚。 - Net:网络

- Reference:引用的模块名称。

约束要加到对象上。

1.4 时序路径

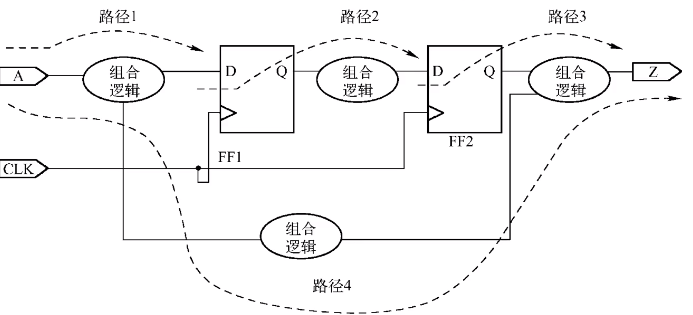

有四种时序路径:

Clock–>D(对应路径2)Clock–>Output(对应路径3)Input–>D(对应路径1)Input–>Output(对应路径4)

时序路径的延迟等于连线延迟加上单元延迟。其中,单元延迟又等于传输延迟加上逻辑延迟。

1.4.1 两个指标

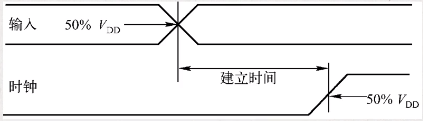

- 建立时间:时钟上升沿之前数据需要稳定的时间。

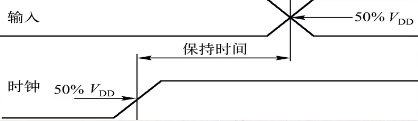

- 保持时间:时钟上升沿之后数据需要稳定的时间。

1.4.2 操作条件

简称PVT。

-

P:Process,工艺。参数 1.0。

-

V: Voltage,电压。一般 1.8 V。

-

T:Temperature,温度。一般 25 ℃。

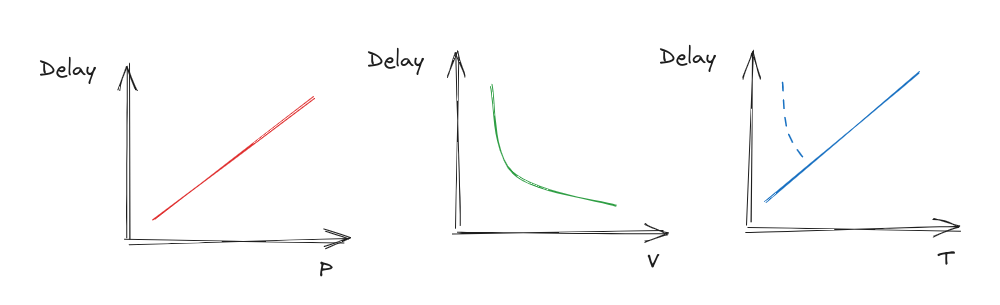

三者和延迟之间的关系如下图:

工艺库中会提供集中工作条件的模型供设计者选择。分别是最好情况、典型情况、最差情况。一般综合只需要考虑两种情况:最差情况用于作基于建立时间的时序分析;最好情况用于作基于保持时间的时序分析。

1.5 流程

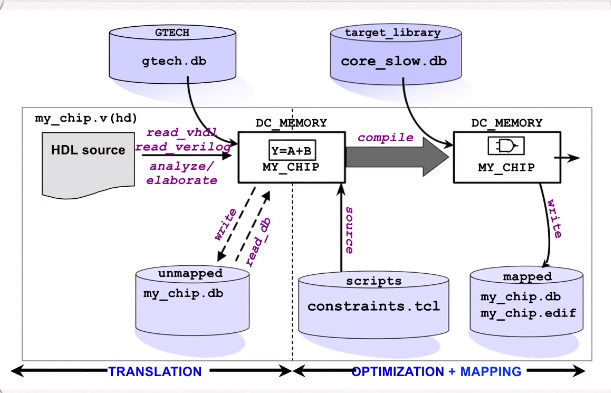

使用synopsys的DC(Design Compiler)作为综合的过程,整个过程可以分为一下几个部分:

- 预综合部分:在综合之前的一些为综合作准备的工作。DC启动;设置各种库文件;创建启动脚本文件;读入设计文件;DC中的设计对象;各种模块的的划分;模块编码。

- 施加设计约束

- 设计综合

- 后综合部分

2 标准工艺库

- 目标库

- 链接库:设置模块和单元电路的引用。DC中年可能用到的库,以及要用到的IP。要注意设置搜索路径。

- 符号库:定义了单元电路显示的schematic的库。

- 算术运算库:实现加法,乘法等运算符。

通常情况下是前三种,最后一种需要license。

链接库和目标库的区别:

链接库对应的是购买的付费IP,存储器,IO以及PAD。

目标库更多指的是标准单元

2.1 时序模型

2.1.1 线性时序模型

两个参数的线性函数:输入转换时间和输出负载电容

$$

D = D_0 + D_1 \times S + D_2 * C

$$

其中,$D_0$、$D_1$和$D_2$是常熟,$S$是输入转换时间按,$C$是输出负载电容。

线性模型不准确。

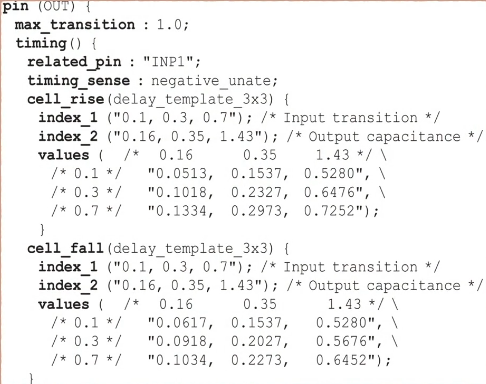

2.1.2 非线性时序模型

二维查找表

分别表示上升延迟以及下降延迟。

若查找值不在表中,我们可以使用插值的方法获取到值。(甚至是高斯消元

XD)

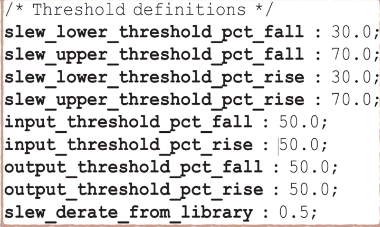

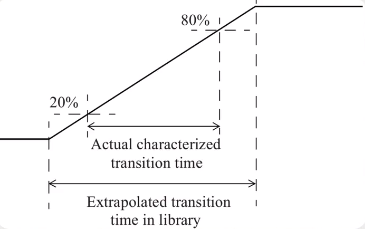

2.1.3 slew值

指定了基于库中指定的测量阈值。目前技术,普遍在30%到70%区间。

上图所示,实际的外推值范围是$\frac{70 – 30}{90 – 10} = 50\%$,即10%到90%。

下图是一个示例。

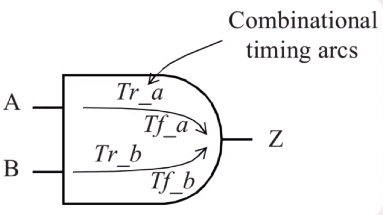

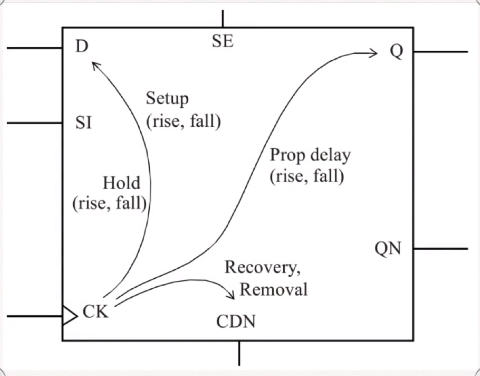

2.1.4 时序模型

- 组合单元

- 时序单元

时序单元更加复杂,有建立时间和保持时间(CK->D),有个传输延迟(CK->Q),有个恢复时间(CK->CDN)。

3 时序约束

DC 是一个约束驱动的综合工具,它的综合结果是跟设计的施加的一些时序越苏条件密切相关的。如果发现不满足时序约束的要求,我们需要重新修改 RTL 代码,然后再来做综合,直到时序满足要求。

3.1 面积约束

使用命令set_max_area对电路的最大面积进行约束。面积约束的定义有三种方式:第一种是两输入与非门的个数;第二种是晶体管的个数;第三种是平方微米。

如何确定命令中 100 的含义?

方法:综合一个两输入与非门,然后

report_area。最后的结果有三种情况:

- 结果是 1:则就是第一种情况,将与非门的大小作为单位 1。

- 结果是 4:则是第二种情况,将晶体管的数目为单位 1。

- 其他值:则就是表示实际的面积,为第三种情况。

3.2 时钟约束

我们必须约束(1)时钟源(2)时钟周期。我们可以选择约束(1)占空比(2)偏移 / 阈值(3)时钟名。我们可以对时钟设定 DontTouch,以告知 DC 不需要对时钟网络进行处理。

3.3 输入延迟

输入延迟是指外部的触发器的 CLK 端到模块输入的延迟。可以使用命令set_input_delay来约束。

3.4 输出延迟

输出延迟可以使用 $D{output} = T{clock} – T{clkq}- T{conb}$ 来计算。表示使用时钟周期减去触发器 clk 到 q 端的延迟,再减去模块外部组合逻辑的延迟。

3.5 DRC 约束

DRC 通常有三种:

set_max_transition:约束设计中的信号、端口、net 的最大翻转不能超过这个值。set_max_fanout:对 design、net、output port 进行操作,表示单元输入引脚相对负载的数目。set_max_capacitance:基于工艺库的信息进行设定。

3.6 环境约束

参考第 1.4 节。

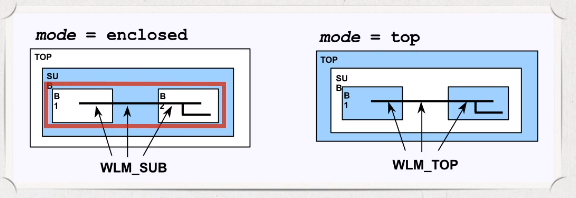

3.7 连线模型约束

连线负载模式共有 3 种,围绕(enclosed)、顶层(top)以及分段(segmented)。

4 逻辑综合常见的优化方式

DC 进行优化的目的是权衡时序和面积的约束,以满足用户对功能、速度和面积的要求。

两种约束:DRC 和 OC。其中 DRC(Design Rule Constraint)如 3.5 节所描述;OC(Optimization Contraint)为优化约束,包括延迟和面积两个方面。DC 会优先满足 DRC 约束。

DC 有很多优化策略:对数据通道的优化,对状态机的优化,对布尔逻辑的优化等等。

参考资料

MOOC芯动力-硬件加速设计方法

B站数字集成电路时序分析基础